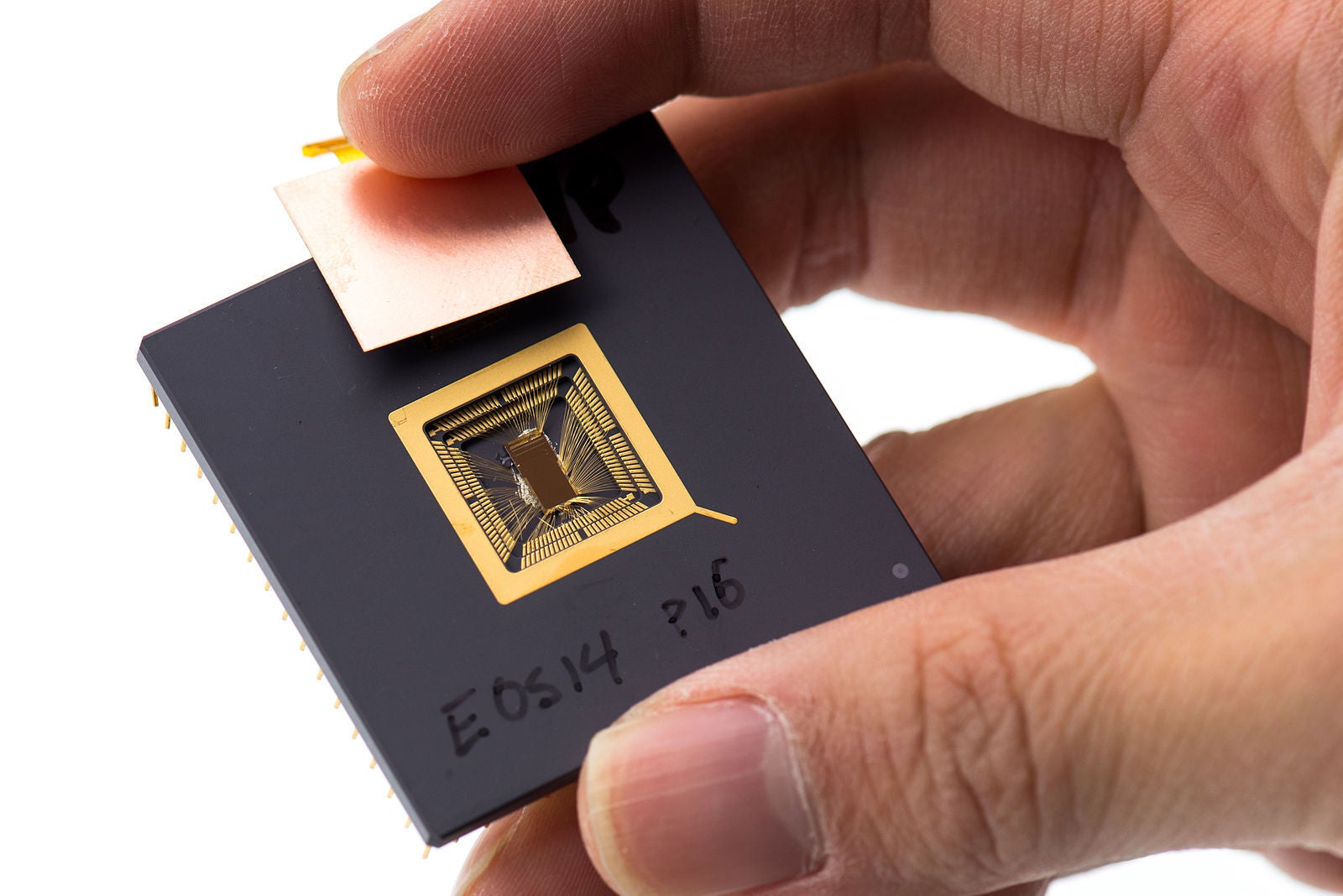

פוסט עלקריירה באתר אפלעשוי לתת לנו רמז לגבי התוכניות העתידיות של אפל לגבי השבבים שבהם היא משתמשת כדי להניע את המכשירים שלה. נכון לעכשיו, החברה מסתמכת על ארכיטקטורת השבבים של ARM Holding עבור ערכות השבבים שלה, אך ענקית הטכנולוגיה מחפשת מתכנת RISC-V בעל ביצועים גבוהים. RISC מייצג מחשב מערך הוראות מופחת והוא ארכיטקטורת שבבים בקוד פתוח.

פרסום דרושים של אפל מרמז על השימוש בארכיטקטורת RISC-V בשבבים עתידיים

מכיוון שהוא בקוד פתוח, יצרני מכשירים שמשתמשים בו לא צריכים לשלם תמלוגים או דמי רישוי. נכון לעכשיו, אפל כן משלמת תמלוגים כדי להשתמש בארכיטקטורה של ARM. בעוד ש-RISC-V מספק חיסכון בצריכת אנרגיה, הוא גם אינו תומך ברמת הביצועים שאתה רואה עם ARM. מלבד היותו חסכוני יותר בצריכת החשמל, RISC-V יכול להוזיל את עלויות ייצור השבבים; עם כל הרכיבים מבוססי ARM המשמשים במכשירים הרבים של אפל, שימוש ב-RISC-V בקוד פתוח יכול לחסוך לאפל מיליוני דולרים בכל שנה.

אפל מפרסמת רשימת משרות המרמזת על השימוש בחלופה של קוד פתוח לצ'יפים מבוססי ARM

אבל זה לא יהיה מעשי עבור אפל להחליף לחלוטין את ערכות השבבים המבוססות על ARM כמו ה-SoCs מסדרת A ו-M ברכיבי RISC-V. זה בגלל שמהלך כזה ייקח שנים של תכנון ותַפּוּחַככל הנראה היה עושה מהלך כזה לפני שהחלה לעבור ל-Apple Silicon עבור מחשבי המק והאייפד פרו. עם זאת יש לציין כי שבבי ARM הם RISC ולמעשה, ARM מייצג Advanced RISC Machine.

באתר של ARM, הוא מגדיר את RISC כ"ארכיטקטורת מיקרו-מעבד המשתמשת בסט קטן ומוטב ביותר של הוראות במקום קבוצת ההוראות המתמחה ביותר שנמצאת בדרך כלל בארכיטקטורות אחרות. RISC מהווה חלופה לארכיטקטורת Complex Instruction Set Computing (CISC) ולעתים קרובות נחשבת לטכנולוגיית ארכיטקטורת ה-CPU היעילה ביותר הקיימת כיום."

RISC-V מציע ביצוע יעיל ומהיר יותר של הוראות המעבד

ARM מוסיפה כי "עם RISC, יחידת עיבוד מרכזית (CPU) מיישמת את עקרון עיצוב המעבד של הוראות פשוטות שיכולות לעשות פחות אבל יכולות לבצע מהר יותר. התוצאה היא שיפור בביצועים. תכונה מרכזית של RISC היא שהיא מאפשרת למפתחים להגדיל את רשום הגדר והגדל את המקביליות הפנימית על ידי הגדלת מספר השרשורים המקבילים המבוצעים על ידי ה-CPU והגדלת המהירות של הוראות ההפעלה של ה-CPU, או "Advanced RISC Machine". משפחה ספציפית של ארכיטקטורת ערכות הוראות המבוססת על ארכיטקטורת ערכת הוראות מופחתת שפותחה על ידי Arm Ltd."

באשר לרשימת המשרה, כותבת אפל, "קבוצת Vector and Numerics מוטלת על המשימה לעצב, לשפר ולשפר מערכות משנה משובצות שונות הפועלות ב-iOS, macOS, watchOS ו-tvOS. הקבוצה מחפשת מתכנת יוצא דופן בביצועים גבוהים כדי להשלים את הצוות ולעשות את ההבדל כחבר בקבוצה המהירה שלנו, תהיה לך הזדמנות ייחודית לשמח ולעורר השראה במיליוני לקוחות של אפל מדי יום."

אם אתה שוקל תפקיד זה, אפל מפרטת את הכישורים:

- 5+ שנים פיתוח אלגוריתמי ברמה נמוכה בעיבוד אותות או פרימיטיבים של למידת מכונה.

- ידע מפורט בארכיטקטורות של ערכת הוראות RISC-V (ISA) ו-ISA וקטור של ARM.

- הבנה מעמיקה של יעילות חישובית.

- כישורי קידוד מצוינים ב-ASM ו-C.

- יכולות תקשורת בכתב ובעל פה חזקות.

- יכולת ניהול משימות מרובות ותעדוף עצמי.

ברור שעבודה כזו דורשת רקע חינוכי חזק במתמטיקה, מדעי המחשב והנדסת מחשבים. בעוד שתואר מתקדם הוא המועדף, ייתכן שתוכל לתפוס את העבודה בלעדיו.

RISC-V חסכוני יותר באנרגיה, משתמש בפחות טרנזיסטורים ומאפשר למשתמשים לבנות שבבים זולים יותר

למרות שאפל לא נראית מוכנה לבצע שינוי סיטונאי ל-RISC-V, היא עשויה להחליט להחליף חלק מהשבבים שנבנו ב-ARM בשבבים חדשים המבוססים על RISC-V. בלי קשר למה שהיא מתכוונת, אפל אכן מחפשת מישהו שיכול לעזור לה לעבוד עם ארכיטקטורת הקוד הפתוח. בתיאור התפקיד נכתב כי "המתכנת יעבוד בצוות ש"מיישם פתרונות RISC-V חדשניים ושגרות מתקדמות. זאת כדי לתמוך בחישוב הדרוש לדברים כמו למידת מכונה, אלגוריתמי ראייה, אותות ו עיבוד וידאו."

לדברי ARM, "RISC מספק ביצועים גבוהים לוואט עבור מכשירים המופעלים על ידי סוללה שבהם יעילות אנרגטית היא המפתח... עבור מעצבי שבבים, מעבדי RISC מפשטים את תהליך התכנון והפריסה ומספקים עלות נמוכה יותר לשבב בשל הרכיבים הקטנים יותר הנדרשים. בגלל מערך ההוראות המופחת והלוגיקה הפשוטה של פענוח, נעשה שימוש בפחות שטח שבב, נדרשים פחות טרנזיסטורים, ויותר אוגרים לשימוש כללי יכולים להשתלב ביחידת העיבוד המרכזית."