בית היציקה הגדול בעולם שייך ל-TSMC של טייוואן. זו החברה שהופכת את עיצובי השבבים של אפל לשבבים ממשיים כמו ה-A15 Bionic (המריץ את סדרת האייפון 13 וכולל 15 מיליארד טרנזיסטורים בכל שבב). TSMC אחראית גם על קו השבבים M1 הכולל את ה-M1 Ultra המופעל על ידי 114 מיליארד הטרנזיסטורים שלו. ה-M1 Ultra מיוצר על ידי שילוב של שני שבבי M1 Max.

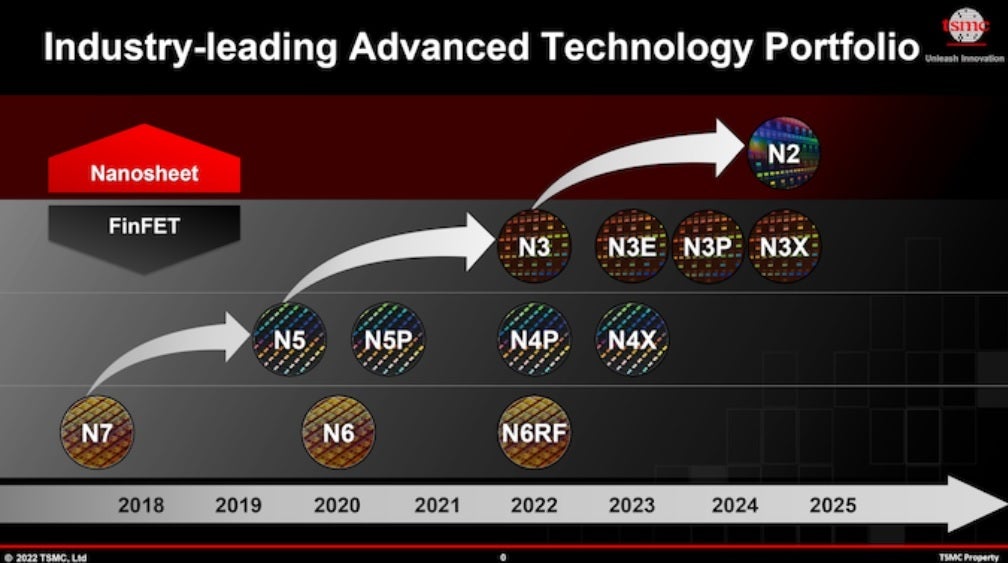

מוקדם יותר השבוע, החל סימפוזיון הטכנולוגיה של TSMC לשנת 2022 שכלל את שחרור מפת הדרכים של TSMC עבור צמתי התהליך המובילים שלה הכוללים שבבי 3nm (N3) ו-2nm (N2). ככל שצומת התהליך קטן יותר, כך גדל מספר הטרנזיסטורים המשמשים בתוך שבב. וזה חשוב כי באופן מסורתי, ככל שספירת הטרנזיסטורים גבוהה יותר, כך השבב חזק וחסכוני יותר באנרגיה.

צומת התהליך העיקרי הבא יהיה 3nm שבו אפל מקווה להשתמש בסדרת האייפון 15 של השנה הבאה. TSMC מצפה שיהיו חמישה צמתים N3 במהלך שלוש השנים הקרובות. במקום לשחרר צומת חדש כל שנתיים, שהיה נהוג למפעל היציקה והתעשייה, TSMC תציג כעת צומת חדש כל שנתיים וחצי גדל לכל שלוש שנים עם צומת התהליך N2 (2nm). נתונים אלה ידועים כקצב הקדנציה של הצומת.

מפת הדרכים של TSMC

TSMC תמשיך להשתמש בטרנזיסטורי אפקט שדה FinFET עבור צומת התהליך שלה ב-3 ננומטר, בעוד שסמסונג תציג לראשונה את טרנזיסטורי ה-gate-all-around שלה עם שבבי ה-3nm שלה). מצד שני, TSMC לא יתחיל להשתמש בטרנזיסטורי gate-all-around עד שהיא תתחיל לשלוח את השבבים 2nm שלה. TSMC מתמחים בתכנון השבבים החדישים יותר של לקוחותיה לדרוש במהירות N2 כאשר זמין, בעוד שהלקוחות הפחות תובעניים לטכנולוגיה של בית היציקה יחליטו כנראה להישאר עם צומת תהליך של 3nm בשנים הקרובות.

צומת ה-3 ננומטר הראשון של היציקה שיישלח יתחיל בייצור בנפח גבוה במהלך המחצית השנייה של השנה. משלוחים של שבבים 3nm יתחילו להתבצע בתחילת 2023. לפיאננדטק, N3 מיועד לאימוצים מוקדמים כוללתַפּוּחַמי יכול לנצל את הגידול בביצועים, הכוח והשטח (PPA) שמסופקים על ידי צמתים מובילים.

הצומת N3E מפחית את צריכת החשמל ב-34%, או מספק עלייה בביצועים של 18%. עד 2024, בית היציקה מצפה להציע את צומת ה-N3P שלה תוך התמקדות בשיפורי ביצועים. ו-N3S היא הגרסה ממוקדת הצפיפות של הצומת 3nm. הצפיפות אומרת לנו כמה מיליון טרנזיסטורים יכולים להתאים למ"מ מרובע של שטח. שבבים בצפיפות גבוהה מאפשרים להציב יותר מעגלים על שבב תוך אספקת מהירות פעולה גבוהה יותר.

צמתי התהליך של 3nm יהיו האחרונים מ-TSMC לספק את צמתי התהליך מבוססי טרנזיסטור FinFET. טרנזיסטורים אלה משתמשים בעיצוב המעוצב כמו "סנפיר" ושם הם מקבלים את שמם. TSMC תציג את טכנולוגיית ה-2nm process node שלה בשנת 2025.